在當今高速發展的集成電路(IC)設計領域,精準、高效的設計規則檢查(DRC)顯得尤為關鍵。不僅保證設計符合製造工藝要求,更是提升良率、縮短迭代、降低成本的關鍵一步。

1、為什麼DRC是IC設計的“把關者”?

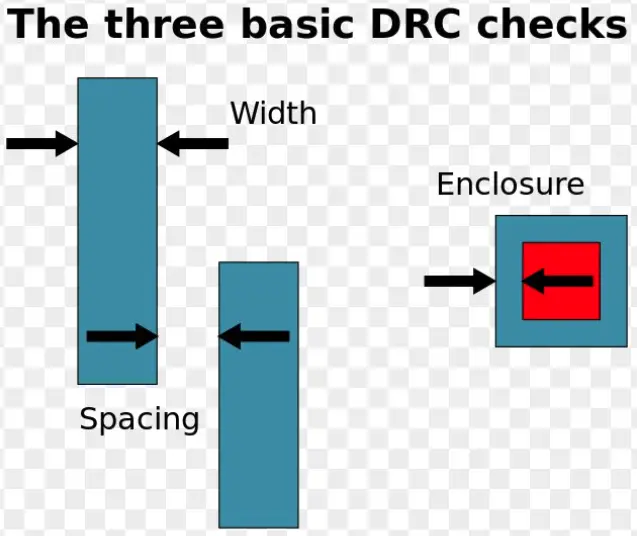

DRC是物理驗證流程中的核心環節,用於檢測佈局是否滿足製造廠商制定的幾何設計規則,如最小線寬、間距、包覆等。早期發現問題,可以大幅減少返工代價,保障產品可靠性與產出率。正如業界所言:“DRC ensures the design meets manufacturing requirements and will not result in a chip failure.”

2、四大高級DRC技術,精進你的設計流程

I. 分層DRC(Hierarchical DRC)

通過階層級別驗證,提高驗證效率與可擴展性。Nvidia 團隊以自定義腳本結合 Verdi 工具,實現了從 RTL 到門級的邏輯、時鐘、功耗與 DFT 並行檢查,藉助 GUI 界面將錯誤定位與設計背景結合,顯著加快調試速度。

行業工具如 Dracula 及 P3 工具支持分層或增量 DRc,進一步實現高效驗證。

II. 自動化DRC修復

工具如 BindKey 的 RDC(Rapid Design Clean)與 RDF(Rapid Design Fix)嵌入 Cadence Virtuoso,可提供在線 DRC 檢查與圖形化提示、自動修復功能,有效提升驗證速度與設計產出質量。

III. 物理感知型DRC(Physically Aware DRC)

DRC 中融入物理約束,例如佈線擁堵、層間耦合等因素。Synopsys Hercules 與 Mentor Graphics Calibre 等支持物理數據庫集成與高效交互的工具,提升了檢測準確性和效率。

IV. 功耗感知型DRC(Power-Aware DRC)

針對低功耗高性能設計,DRC 需兼顧功率完整性檢查。Mentor Graphics 的 Calibre 可進行功耗規則檢查,確保多閾值單元、時鐘門控等低功耗技術的規範合規性。

此外,Calibre 更支持電壓感知(Voltage-Aware DRC),根據電壓域實現上下文感知的間距驗證,極大提升可靠性和良率。

3、四技助你穩中求進

技術手段 核心優勢

分層DRC 快速定位問題、節省重驗證資源

自動化DRC修復 提升驗證效率、減少人為操作負擔

物理感知DRC 更貼合實際佈局,提高錯誤捕獲精度

功耗感知DRC 保證低功耗設計同時滿足性能要求

這些高級DRC方法讓IC設計驗證更智能、更快速、更可靠,是邁向高可靠、高效設計的重要方向。

4、智慧學習,從EDA Academy開啓

如果你也希望在IC設計與DRC驗證領域具備這些前沿技能,EDA Academy(www.eda-academy.com)是你的理想起點:

擁有 海量、專業、全面、最新 的網課內容,涵蓋分層 DRC、自動化修復、功耗感知驗證等高級主題;

用户可 註冊為導師,分享經驗並獲得授課機會;

也能 免費註冊郵箱訂閲,定期獲取行業資訊與學習資源;

更可加入 銷售聯盟計劃,推薦課程可賺取 20%–50% 佣金。

無論你是初學者還是在職工程師,都能找到匹配的成長路徑。讓ED A Academy成為你職業提升的加速器!

5、技術+平台加速你的IC設計驗證進階之路

從分層DRC、自動化修復、物理 & 功耗感知DRC,到 EDA Academy 的學習資源支持,一站式助你把握行業前沿,提升驗證效率與設計質量。