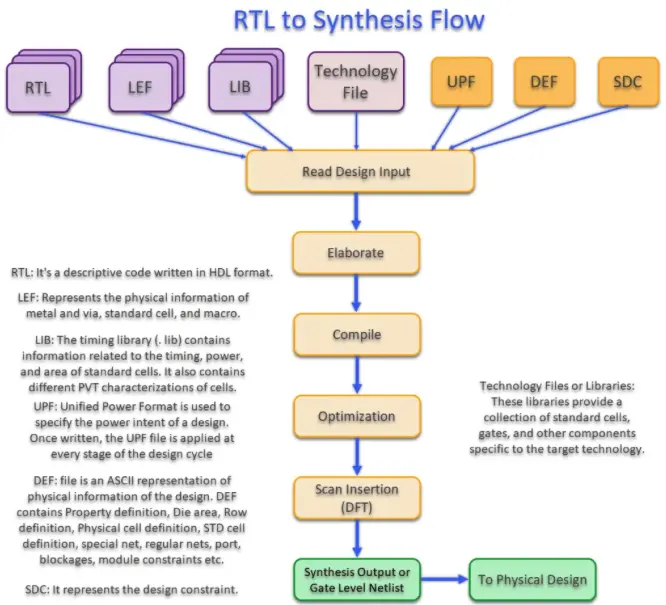

在現代 IC 設計流程中,RTL 合成扮演着至關重要的橋樑角色:將程序員或設計者編寫的 RTL 描述(多用 Verilog/VHDL 編寫)轉化為符合工藝庫的門級 netlist,從而實現後續的物理實現和驗證。

1、RTL 合成關鍵流程解析

合成階段 説明

Technology Mapping(技術映射) 選擇目標工藝庫中的標準單元(如與門、觸發器、多路選擇器等)來實現 RTL 中的邏輯模塊。

Logic Optimization(邏輯優化) 利用布爾最簡、冗餘移除等手段,縮減面積、降低延遲與功耗,提升綜合效果。

Timing Analysis(時序分析) 分析關鍵路徑,確保設計滿足時鐘約束,避免違例,提高設計健壯性。綜合最佳實踐 編寫兼容綜合器的 RTL 代碼、使用合成指令優化輸出、頻繁運行綜合並調整策略預防問題積累。

2、為什麼 RTL 合成如此重要?

它是設計抽象與物理實現之間的核心連接過程,是芯片從“邏輯意圖”走向“物理現實”的關鍵步驟。

合成質量直接決定了芯片的功耗、面積和時序表現,影響最終產品的性能和成本。

隨着設計規模不斷擴大,合成工具也趨於智能化,未來可能引入機器學習優化策略、融合功耗意識傳播(power-aware synthesis)等先進技術,使設計效率和質量更進一步提升。

3、為什麼推薦 EDA Academy 學習 RTL 合成?

要深入掌握 RTL 合成並具備實戰能力,推薦訪問 EDA Academy (www.eda-academy.com) ——為 IC 行業量身打造的綜合在線學習平台:

· 課程覆蓋全面:包括 RTL 合成流程理論、優化技巧、時序收斂實踐,以及主流工具(如 Cadence Genus、Synopsys Design Compiler 等)的實操課程。

· 導師機會開放:若你在合成或物理實現領域擁有經驗,也可以註冊成為平台導師,分享你的專業知識與實踐經驗。

· 訂閲獲取資訊:只需郵箱註冊,即可免費訂閲 EDA Academy 的 newsletter,定期獲取最新課程內容及 IC 行業前沿信息。

· 推廣還能賺錢:加入其銷售聯盟計劃,通過分享課程鏈接即可獲得 20%–50% 的佣金,讓你的知識傳播也能產生收益。

RTL 合成是實現高效 IC 設計的核心環節,它涵蓋邏輯優化、技術映射與時序驗證等關鍵技術。如果你想系統學習如何高質量完成 RTL 合成,建議訪問 EDA Academy(www.eda-academy.com),這裏不僅有系統課程和實操指導,還有導師機會、免費 newsletter 與高達 50% 的推廣佣金——真正實現學習、分享、收益三合一。