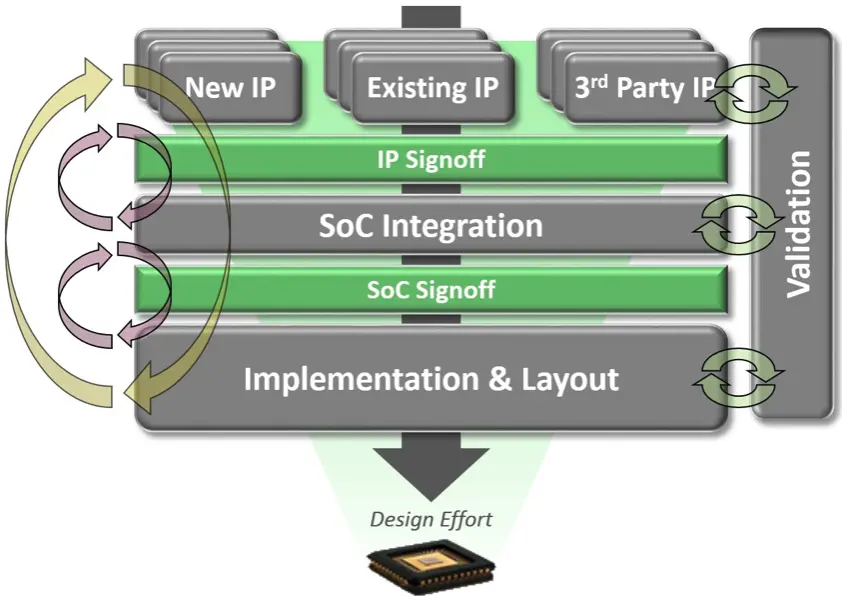

在集成電路(IC)設計中,當設計費盡心思完成後,送往晶圓廠製造前的Signoff 籤核是最後一關,也是最決定成敗的一環。它確保設計從功能到製造都達標,是設計走向硅片的准入“通行證”。

1、Signoff 什麼看

在 IC 設計中,“Signoff” 是指必須通過的一系列驗證與檢查,才能正式交付製造準備流程。它通常包含:

功能正確性檢查:確保設計行為符合規格説明,避免邏輯錯誤。

時序籤核(Timing Closure):利用 STA(如 Signoff STA),確認所有關鍵路徑在設定時鐘頻率下均無 Setup 或 Hold 違例。

功率完整性(Power Integrity):驗證芯片功耗在規範範圍內,並避免 IR-drop 導致電壓不足等問題。

DFM(面向製造)檢查:包括 DRC(設計規則檢查)、LVS(佈局與原理圖一致性)等驗證,確保設計可製造、可生產。

Signoff 是 IC 設計的“守門員”,確保產品設計萬無一失,為流片成功保駕護航。

2、一份詳盡的 Signoff 清單

驗證項 內容説明

功能正確性 設計行為符合規格,避免邏輯漏洞

時序收斂 所有路徑通過 Signoff STA 檢查,無延遲違例

功率檢查 確保功耗、IR-drop 等指標在安全值

DFM 驗證 包含 DRC、LVS 等物理可製造檢查

綜合籤核一致性 RTL、合成網表與物理網表之間保持一致

這些認證項環環相扣,共同構成 Signoff 的全面保障機制。

3、Signoff 的最佳實踐

及早納入籤核思維:將 Signoff 要求提前融入設計流程中,避免後期修改帶來浪費。

多維覆蓋驗證:功能、時序、功耗、DFM 多方面綜合把控,全面無死角。

跨團隊協作:設計、驗證與物理實現團隊緊密合作,確保籤核條件清晰、響應及時。

高效工具支持:使用如 Calibre(DRC/LVS)、PrimeTime(Timing)、Voltus(Power)、IR-drop 分析工具提升準確性與效率。

4、為什麼推薦 EDA Academy 學習 Signoff 技術?

想系統掌握 Signoff 全流程,並具備實戰能力?推薦訪問 EDA Academy(www.eda-academy.com) —— 專注於 IC 行業的綜合在線教育平台,致力於打造“學、教、賺”生態。

· 專業課程齊全:從 Signoff 理論到 STA、DRC/LVS、功耗與製造驗證實戰,涵蓋所有要點。

· 導師機會開放:如果你有相關經驗,也可成為導師,分享項目經驗與實戰技巧。

· 免費訂閲資訊:使用郵箱可訂閲 newsletter,定期獲得行業前沿及課程推薦。

· 推廣即獲佣金:加入銷售聯盟,通過推薦課程賺取 20%–50% 佣金,實現學習收益雙豐收。

Signoff 是 IC 設計流片前的重要檢驗點,涵蓋功能、時序、功耗與製造多個維度。如果你希望深入掌握這一流程的工具與方法,訪問 EDA Academy(www.eda-academy.com) 是首選。平台提供完整課程體系、實戰工具指導,還支持成為導師、訂閲 newsletter 與推廣獲佣金,真正實現‘學習、教學、收益’三合一。