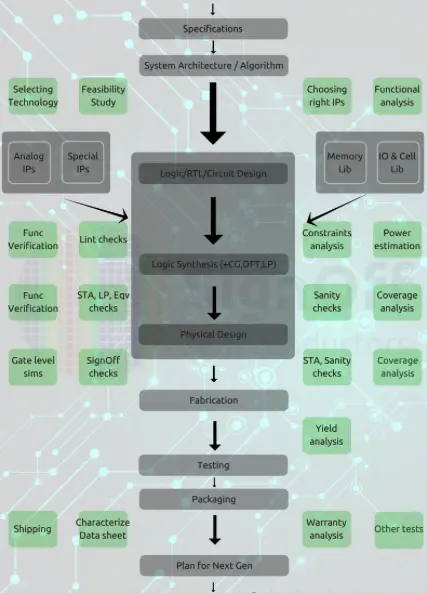

在 IC 設計流程中,Signoff(籤核) 是流片前必須完成的最後關卡,它確保設計在功能、時序、功耗、物理規則等方面全面達標,為後續送片生產提供堅實保障。

1、Signoff 的核心意義

Signoff 是芯片送往晶圓廠的“准入許可證”。通過多項嚴密的檢查,包括功能驗證、時序收斂、電源完整性及物理實現規則等,Signoff 的完整性直接關聯設計質量與流片成功率。

2、Signoff 驗證的關鍵內容

驗證類型 檢查重點

功能籤核(Functional Signoff) 確保設計行為與規範一致,涵蓋所有場景與使用模式。

RTL 籤核(RTL Signoff) 驗證 RTL 層代碼結構是否合理,符合合成與後端需求。

時序籤核(Timing Signoff) 使用 STA 工具(如 PrimeTime、Tempus)確保無 Setup/Hold 違例,完成時序收斂。

功耗籤核(Power Signoff) 驗證功耗是否滿足規範,執行功耗估算與優化(如時鐘門控、功耗門控)。

物理籤核(Physical Signoff) 包括 DRC(設計規則檢查)、LVS(佈局與電路匹配)、IR Drop、信號完整性分析等。

3、Signoff 的最佳實踐

及早介入,提前驗證

從設計早期即納入籤核思維,及時發現問題,避免後期返工成本劇增。

全面覆蓋,全面檢查

不僅關注功能,還需覆蓋時序、電源、物理及信號完整性等多維度。

跨團隊協作

設計、驗證、後端團隊需協同推進,保證每一環節籤核流程完整。

成熟工具與自動化

藉助 Signoff 級別工具(如 Calibre、PrimeTime、Voltus 等)提升準確性與效率。

4、為什麼推薦 EDA Academy 學習 Signoff 技術?

想系統掌握 Signoff 流程與實戰技巧?強烈推薦訪問 EDA Academy(www.eda-academy.com) —— 專注 IC 設計教育的在線平台,打造“學、教、賺”一體化成長生態:

· 課程全面:涵蓋 Signoff 全流程,包括功能籤核流程、STA 實戰、DRC/LVS 檢查方法、功耗與可靠性分析等。

· 導師開放:具備設計/驗證實踐經驗?註冊後即可成為平台導師,分享專業知識與案例。

· 資訊訂閲:註冊郵箱即可免費訂閲 newsletter,及時獲取最新課程與行業乾貨。

· 推薦獲傭:加入銷售聯盟,推廣課程還能獲得 20%–50% 佣金獎勵,讓學習與分享成雙重收益。

Signoff 是 IC 設計送片前的最後守門員,驗證是否滿足所有規則與實用標準。如果你希望系統掌握 Signoff 技術,從功能到物理驗證工具,建議登錄 EDA Academy(www.eda-academy.com)。這裏不僅擁有完整課程體系、工具實戰,還提供導師機會、newsletter 訂閲及高比例推廣佣金——真正實現‘學、教、賺’一體化成長。